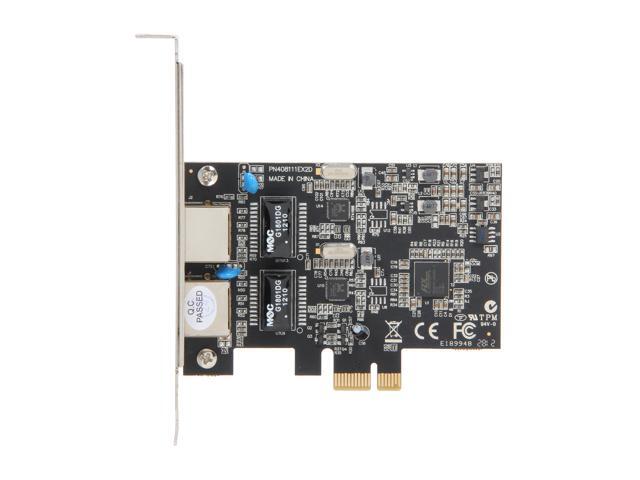

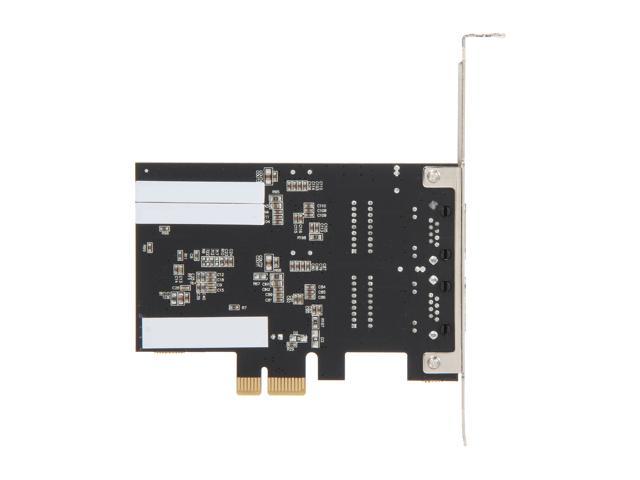

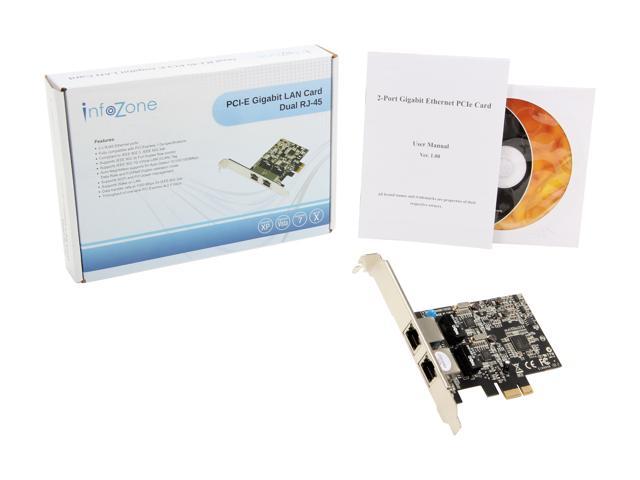

Part Number: SY-PEX24028 The architecture is a cost-effective, low-pin count, and point-to-point technologies offering maximum bandwidth, reducing cost and design complexity and enabling smaller form factors. It provides throughput and connectivity at Gigabit speeds up to 1000 Mbps (1Gbps) raw bandwidth, this is 100 times faster than the original Ethernet, yet it is compatible with existing EthernetRealtek Chipset 8111EDesigned to Meet PCI Express Specification Revision 1.0aSingle-lane (or x1) PCI Express Throughput Supports Rate of 2.5GbpsFully Compliant with IEEE 802.3, IEEE 802.3u, IEEE 802.3ab10/100/1000M Data Auto-negotiationLEDs Indicate the Status of Data TransmissionSupport Wake On Lan (WOL) Power Management (Optional)Full Duplex Mode Doubles the Network Connections SpeedFeatures:Integrated 10/100/1000 transceiverAuto-Negotiation with Next Page capabilitySupports PCI Express 1.1Supports pair swap/polarity/skew correctionCrossover Detection & Auto-CorrectionWake-on-LAN and remote wake-up supportMicrosoft NDIS5, NDIS6 Checksum Offload (IPv4, IPv6, TCP, UDP) and Segmentation Task-offload (Large send v1 and Large send v2) supportSupports Full Duplex flow control (IEEE 802.3x)Supports jumbo frame to 9K bytesFully compliant with IEEE 802.3, IEEE 802.3u, IEEE 802.3abSupports IEEE 802.1P Layer 2 Priority EncodingSupports IEEE 802.1Q VLAN taggingSupports IEEE 802.3az Draft 3.0 (EEE)Embedded OTP memory can replace the external EEPROMSerial EEPROMTransmit/Receive on-chip buffer supportSupports power down/link down power savingBuilt-in switching regulatorSupports PCI MSI (Message Signaled Interrupt) and MSI-XSupports quad core Receive-Side Scaling (RSS)Supports Alert Standard Format 2.0 (ASF2.0)Supports Protocol Offload (ARP & NS)Supports Customized LEDsSupports 1-Lane 2.5Gbps PCI Express BusSupports hardware ECC (Error Correction Code) functionSupports hardware CRC (Cyclic Redundancy Check) function