AMD has spent the last several years turning 3D V-Cache from an experimental concept into the defining feature of high-performance desktop computing. With the launch of the AMD Ryzen 9 9950X3D2 Dual Edition in 2026, the company has taken its most dramatic step yet — stacking 3D V-Cache on not one, but both compute chiplets. The result is a processor architecture unlike anything previously available in the consumer or prosumer desktop market.

This article focuses on what makes the 9950X3D2’s architecture fundamentally different — and why the “Dual” designation changes more than just a number.

What Is 3D V-Cache, and Why Does It Matter?

3D V-Cache is AMD’s brand name for vertically stacked SRAM — a layer of high-speed cache memory bonded directly on top of the CPU’s compute die using through-silicon via (TSV) interconnects. Unlike traditional cache that lives on the same silicon plane as the processing cores, 3D V-Cache sits above the dies, creating a true three-dimensional memory architecture.

The result is enormous on-package cache capacity at extremely low latency. Cache memory is the fastest storage tier a processor can access — closer and faster than DRAM by orders of magnitude. When a game, simulation, or AI workload fits within the on-chip cache, the processor avoids the latency penalty of reaching out to system DRAM entirely.

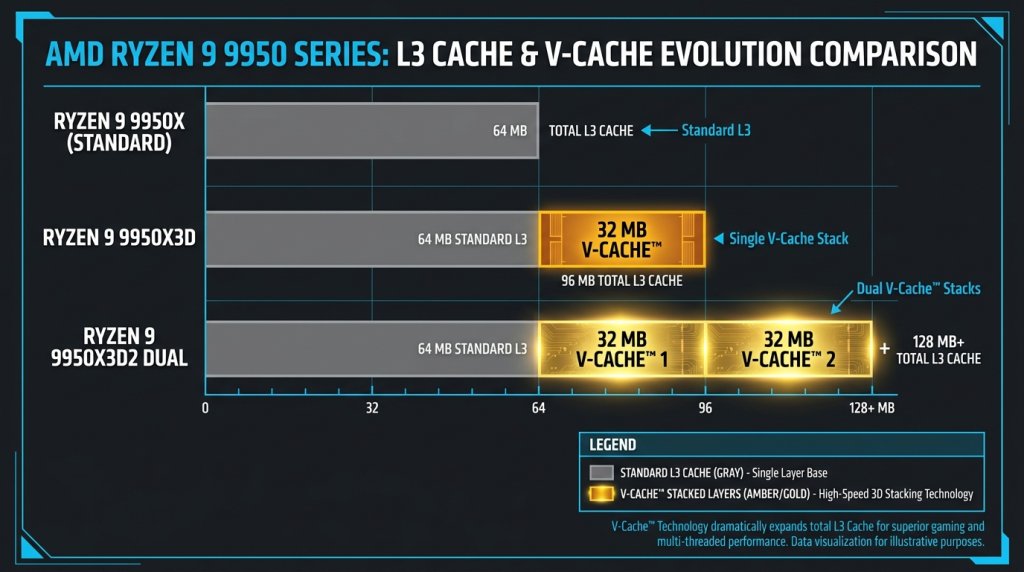

The first 3D V-Cache chips — starting with the Ryzen 7 5800X3D — proved the concept definitively. The 9950X3D, launching in the 9000 series Granite Ridge generation, extended it to a 16-core processor. The 9950X3D2 Dual Edition takes the logical next step: applying 3D V-Cache stacks to both CCD (Core Chiplet Dies) simultaneously.

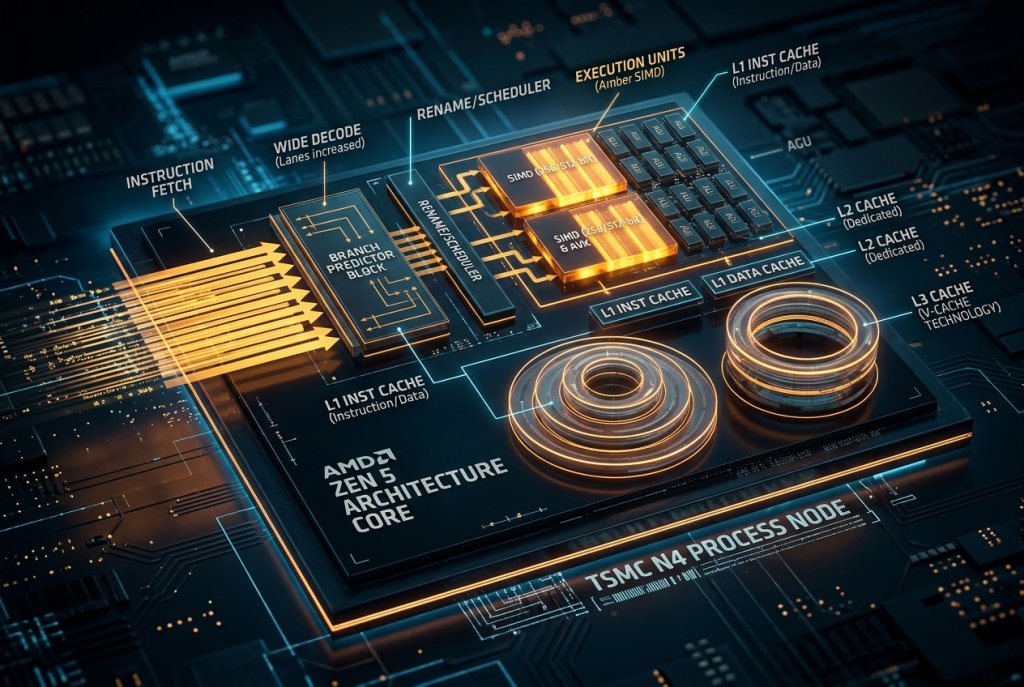

The Granite Ridge Foundation: Zen 5 Architecture

The 9950X3D2 is built on AMD’s Zen 5 microarchitecture — the same core design used across the Ryzen 9000 series. Zen 5 introduces several meaningful improvements over Zen 4:

- Wider front-end: Expanded instruction fetch and decode bandwidth reduces pipeline stalls under complex workloads

- Improved branch prediction: Reduces misprediction penalties in workloads with irregular control flow

- Enhanced floating-point units: Larger SIMD execution units accelerate multimedia, scientific, and AI inference workloads

- TSMC N4 process node: Higher transistor density and improved power efficiency compared to Zen 4’s N5

On its own, Zen 5 represents a meaningful IPC improvement over Zen 4. Combined with dual 3D V-Cache stacks, it creates a processor that excels not only in single-threaded response but in sustained multi-threaded throughput — the two dimensions that previously competed against each other in X3D chip design.

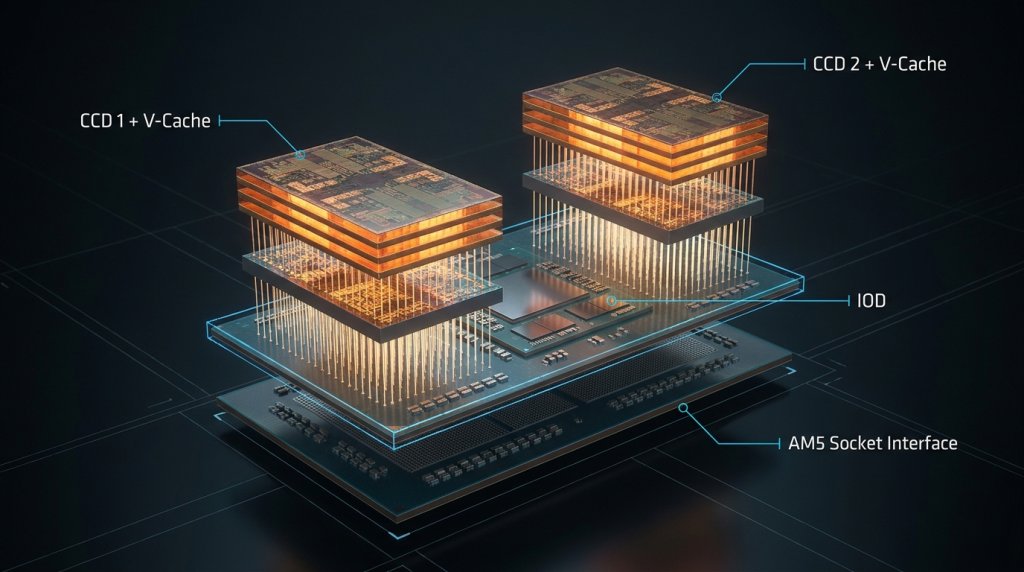

The “Dual” Difference: Two CCD, Two V-Cache Stacks

The standard Ryzen 9 9950X3D uses a dual-CCD layout (two 8-core chiplets for 16 cores total), with 3D V-Cache stacked on one CCD. This created an architectural asymmetry: one CCD had the extended cache advantage; the other operated without it.

For gaming workloads — which typically saturate one CCD at a time — this asymmetry was manageable. AMD’s scheduler learned to route game threads to the V-Cache CCD. But for multi-threaded workloads that span both CCDs, only half of the cores benefited from the cache advantage.

The AMD Ryzen 9 9950X3D2 Dual Edition eliminates this asymmetry. Both CCDs carry a stacked 3D V-Cache layer, giving every core on the processor access to the expanded cache pool. The total L3 cache capacity scales accordingly — delivering a cache-rich environment for workloads that would previously have been “half in” on standard X3D chips.

Cache Architecture Specifications

| Specification | Ryzen 9 9950X (Standard) | Ryzen 9 9950X3D (Single Stack) | Ryzen 9 9950X3D2 Dual Edition |

|---|---|---|---|

| Architecture | Zen 5 (Granite Ridge) | Zen 5 (Granite Ridge) | Zen 5 (Granite Ridge) |

| Cores / Threads | 16C / 32T | 16C / 32T | 16C / 32T |

| L3 Cache | 64MB | 128 MB | 192MB |

| V-Cache CCDs | 0 | 1 of 2 | 2 of 2 |

| Socket | AM5 | AM5 | AM5 |

| TDP | 170W | 170W | 200W |

| PCIe Support | PCIe 5.0 | PCIe 5.0 | PCIe 5.0 |

The jump from 96 MB (single-stack X3D) to 128 MB and beyond (dual-stack X3D2) matters most in workloads that generate large working set sizes — game worlds that stream assets, simulation datasets, EDA (Electronic Design Automation) tools, and increasingly, on-device AI inference models.

AM5 Platform Compatibility: No New Motherboard Required

One of the most strategically significant aspects of the 9950X3D2 launch is its AM5 socket compatibility. Existing AM5 motherboards — including X670E, X670, B650E, and B650 platforms — can support the 9950X3D2 with a BIOS update. This means users already invested in the AM5 ecosystem can upgrade without replacing their entire platform.

AM5 supports:

- DDR5 memory (up to DDR5-6400+ with EXPO/XMP tuning)

- PCIe 5.0 for GPU and NVMe SSD connectivity

- USB4 and USB 3.2 Gen 2×2 through platform chipset

For users building new systems around the 9950X3D2, high-end X670E boards offer the most robust power delivery and overclocking headroom.

The Thermal Engineering Challenge of Dual V-Cache

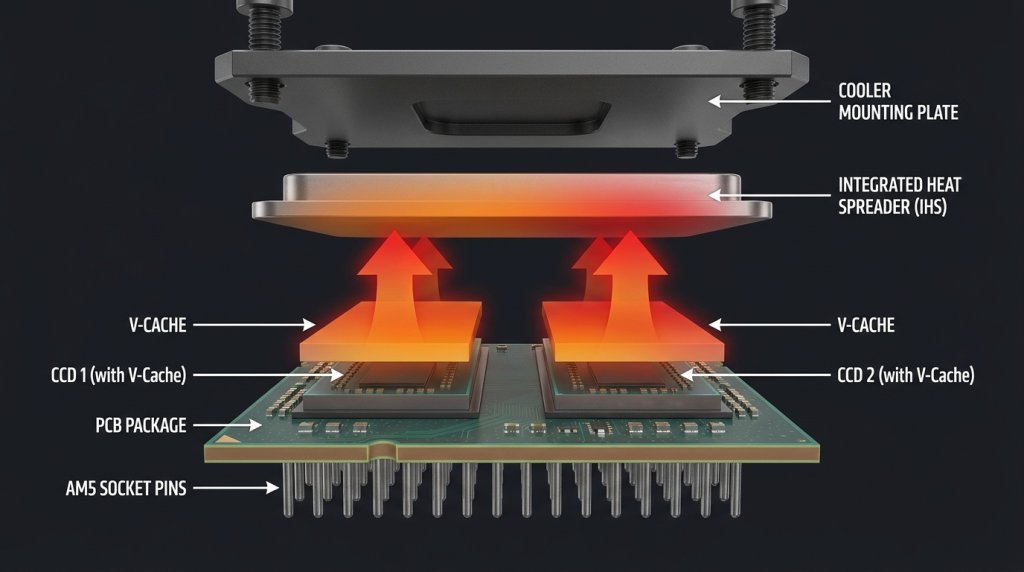

Stacking additional silicon on top of both CCDs introduces a thermal management challenge: the V-Cache layers sit between the compute dies and the IHS (Integrated Heat Spreader), which means heat must travel through two stacked layers before reaching the cooler.

AMD addresses this through refined TSV density, improved thermal interface material between die layers, and conservative power limits that prevent the stacked dies from reaching damaging temperatures under sustained load. The 170W TDP of the 9950X3D2 is maintained by managing boost behavior more conservatively than the non-V-Cache 9950X — a deliberate trade-off that prioritizes sustained throughput over brief peak clock bursts.

This thermal architecture means the 9950X3D2 pairs best with high-performance tower coolers or 360mm+ AIO liquid coolers — not because it runs dramatically hotter, but because sustained performance under heavy workloads is better maintained with robust thermal headroom.

How the 9950X3D2 Fits the 2026 Computing Landscape

The timing of the 9950X3D2 launch aligns with several 2026 computing trends:

On-device AI inference has grown from a background feature to a primary workload for a growing segment of power users. Large language models at the 7B–13B parameter scale — used for local AI assistants, code generation, and document processing — generate working set sizes that benefit enormously from expanded L3 cache.

Game world complexity continues to scale. Open-world titles in 2026 stream significantly larger asset pipelines than equivalent games from 2022–2023, increasing the practical benefit of cache-rich CPU architectures.

EDA and simulation tools — the professional domain where AMD’s EPYC platform has dominated — increasingly seek single-socket performance rather than just core count. The 9950X3D2 brings near-workstation cache performance to the consumer AM5 platform. For context on what full server-class processors look like at scale, the AMD EPYC 9554 represents the data center end of AMD’s architectural DNA — and the 9950X3D2 brings some of that cache-rich philosophy to the desktop.

The Bottom Line

The AMD Ryzen 9 9950X3D2 Dual Edition represents a genuine architectural leap. By extending 3D V-Cache to both compute chiplets simultaneously, AMD has created a processor that eliminates the core-access asymmetry of its predecessors and delivers a symmetrically cache-rich architecture to every thread. Built on Zen 5, compatible with the existing AM5 platform, and supported by AMD’s refined thermal engineering for dual-stack dies, the 9950X3D2 is the most architecturally ambitious desktop processor AMD has launched.

For the full technical specifications and availability, see the official AMD Ryzen 9 9950X3D2 Dual Edition product page and the Newegg listing.